最近有媒体报道台积电准备开始为美国苹果、英伟达公司试产2纳米芯片。

目前的2纳米芯片被公众热议,一个主要原因是2纳米芯片被认为是半导体制造一个里程碑式的节点:它将采用取代十余年前开始主导半导体制造的FinFET的新构架--GAA。

2021年,IBM宣布首发2纳米芯片,目前美国英特尔、中国台湾台积电、韩国三星、日本“Rapidus”都开始追逐2纳米芯片。

2纳米芯片即将量产,那么0.2纳米芯片还有多远呢?今天我们就聊一下这个问题。

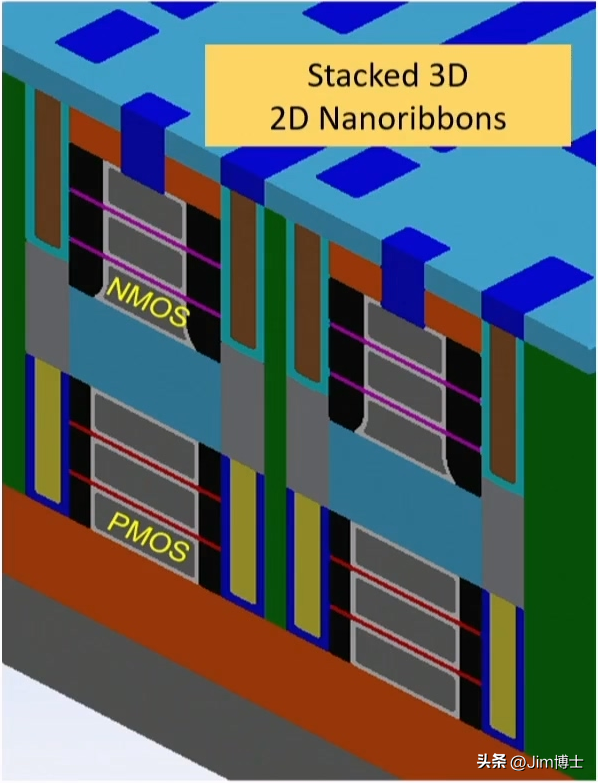

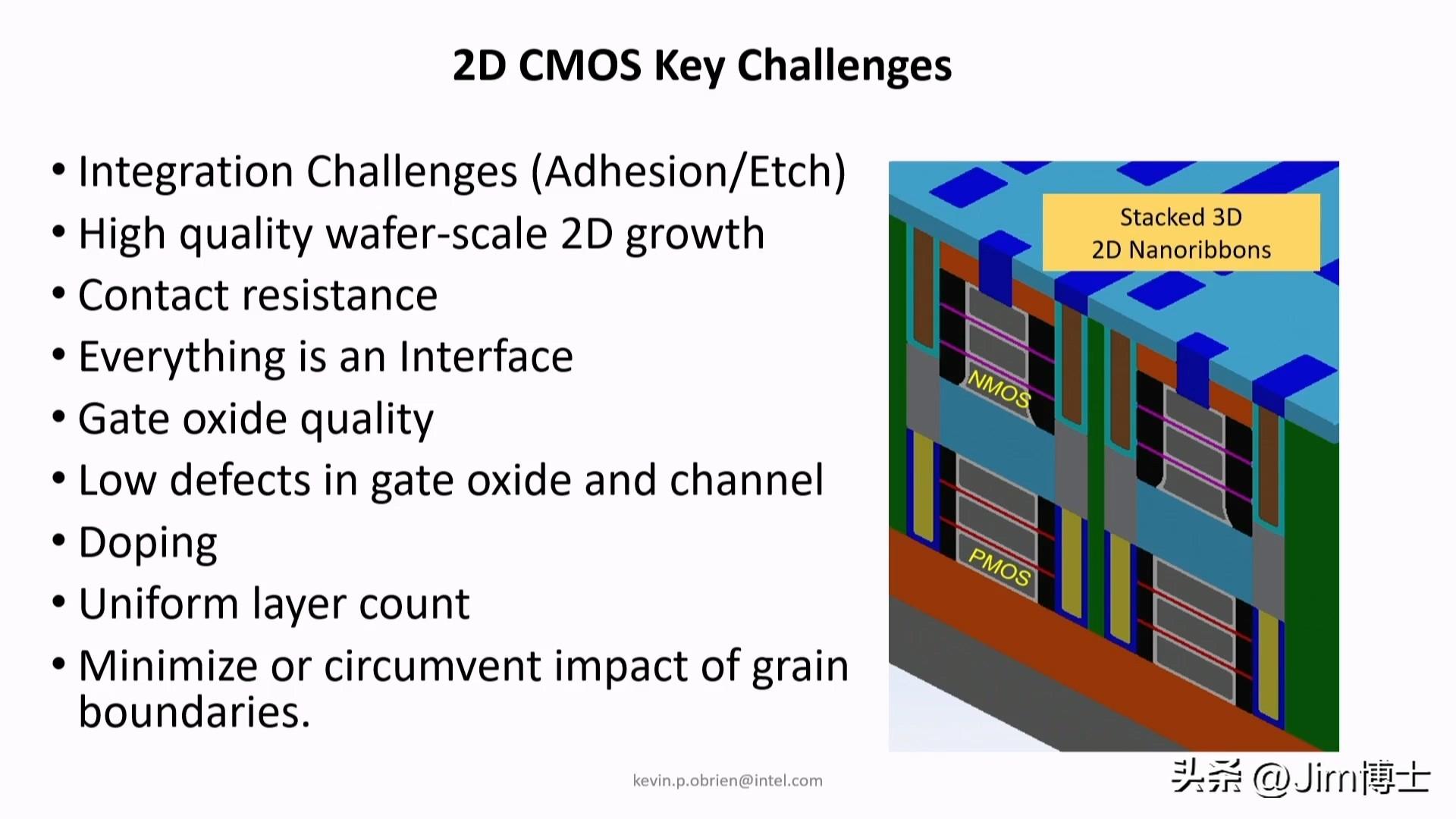

下图展示的就是0.2纳米芯片的一种构架(右侧),我们简单称其为“堆叠2维材料晶体管”。注意图中标注“PMOS”和“NMOS”的红色线和紫色线便是单层2维材料。

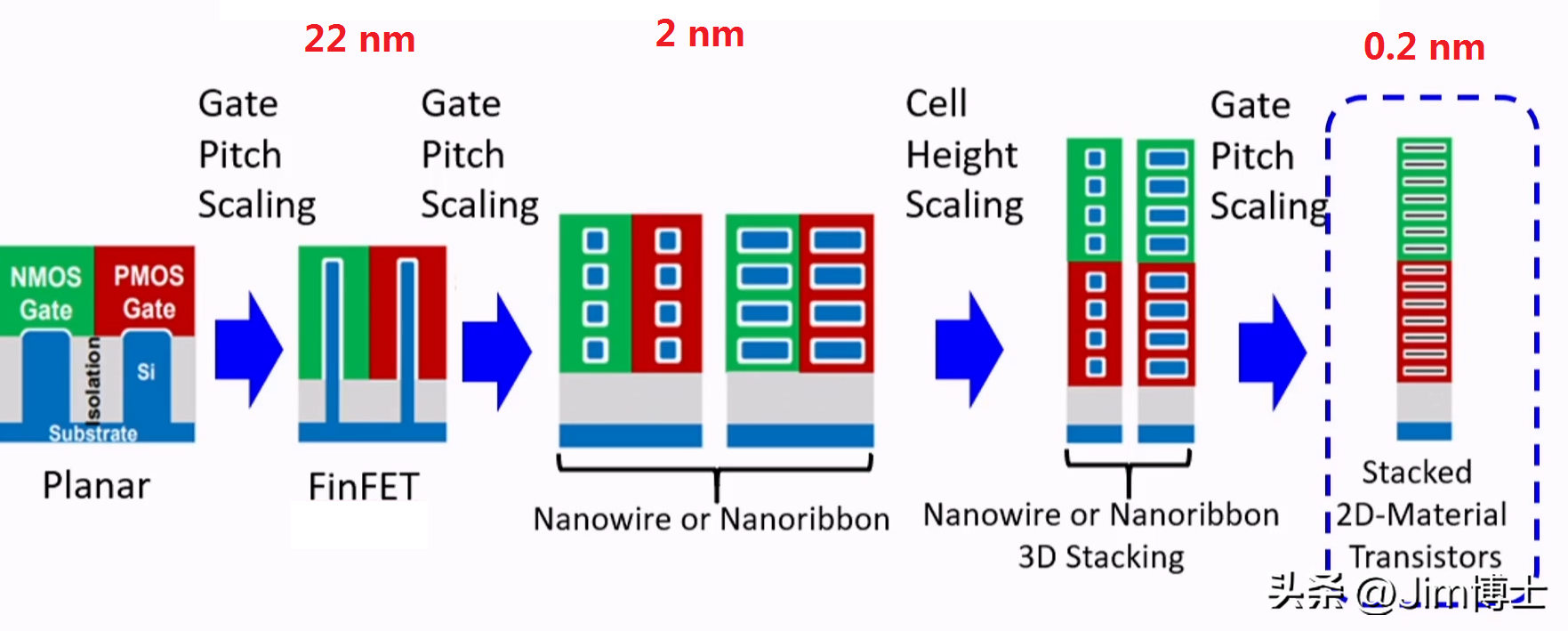

如果单独看它的结构可能不容易理解,不过如果我们展示了从90年代以前的平面晶体管、到21世纪初的三维晶体管(FinFET),一直演变到目前的GAA晶体管,我们就可以容易理解它的演变:

1,从22纳米到2纳米,主要是栅极间距的缩放驱动;

2,从2纳米到0.2纳米,主要是单元高度缩放驱动;

3,而到0.2纳米,则又是在新构架下的栅极间距缩放驱动。

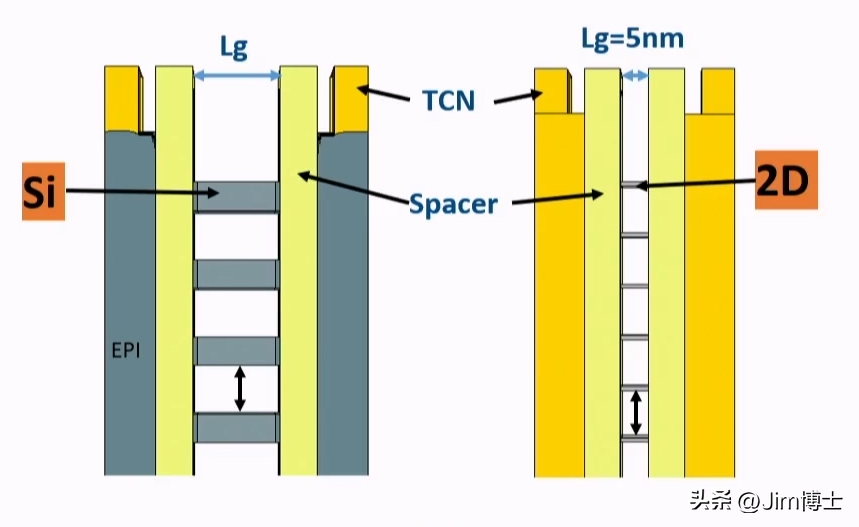

下图对比了在新构架下硅芯片和2D材料所能允许的栅极长度Lg的下限,前者到15纳米以下失效,后者能够支持5纳米。

下图是单个2D半导体晶体管的截面图,它以原子角度的视角来展示单个2D半导体晶体管研究的一些核心部分,包括最核心的2D单层沟道、栅极氧化层、栅极金属层、源漏极接触层等。

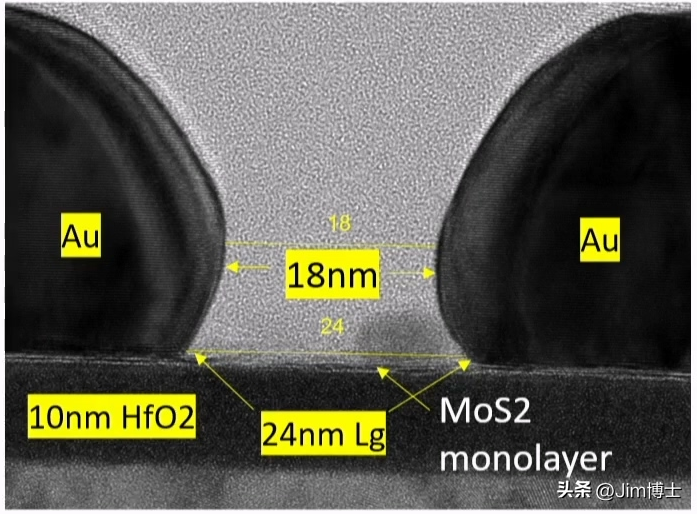

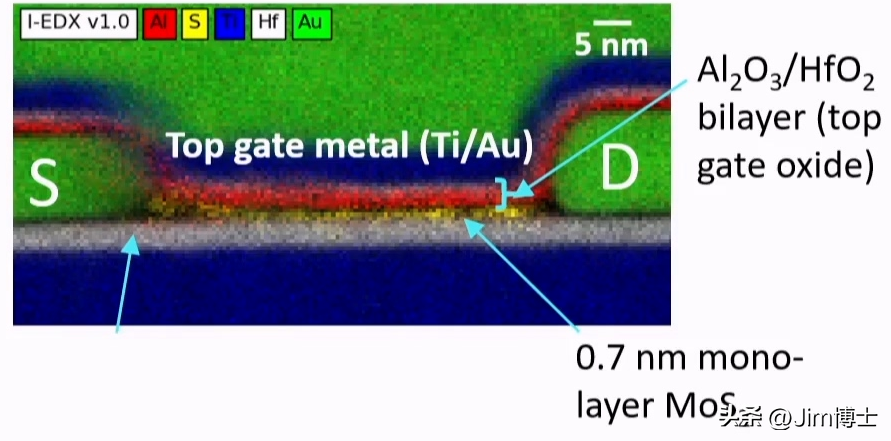

下图是一个2D半导体晶体管的实物电镜图:它的沟道材料MoS2,厚0.7纳米,长24纳米。

我们从元素扫描图上可以更清晰的看到整个2D半导体晶体管的物理结构。

值得一提的是,关于2D半导体晶体管的研究可以说是俯拾即是,为什么呢?

我们从下图就可以看出来,如果只是研究单个晶体管的特性,它本身是非常简单的结构,甚至不需要非常复杂精密的半导体制造技术。

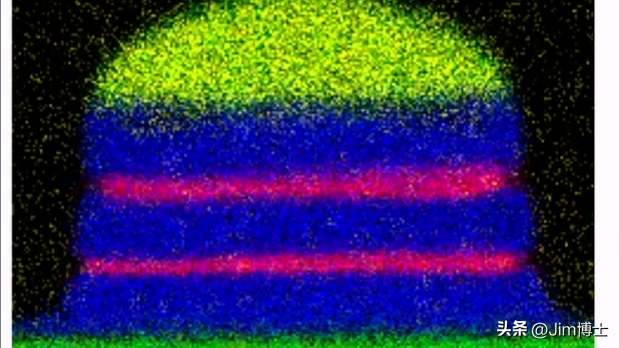

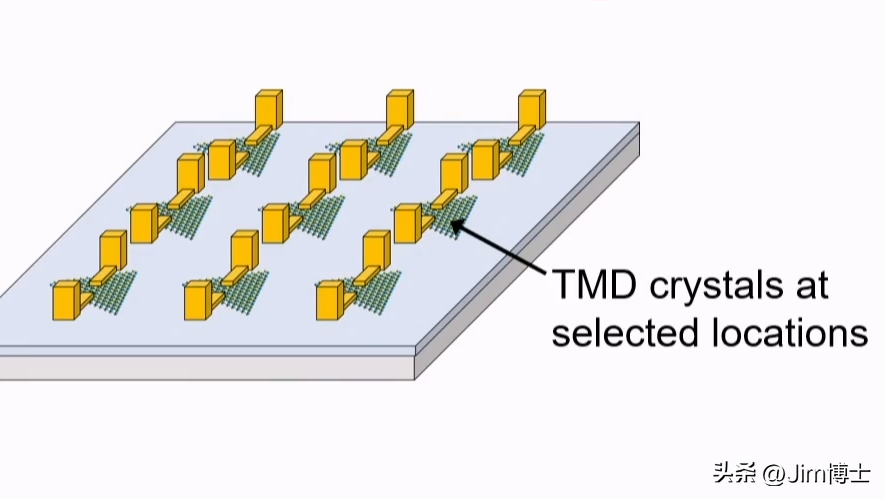

而芯片级的2D晶体管,不仅是尺寸达到10纳米左右,而且要满足大批量3D立体制造,满足半导体制造工艺要求,满足性能匹配的材料,并且满足芯片的极端性能--这种晶圆级芯片的量产制造才是真正的技术瓶颈。

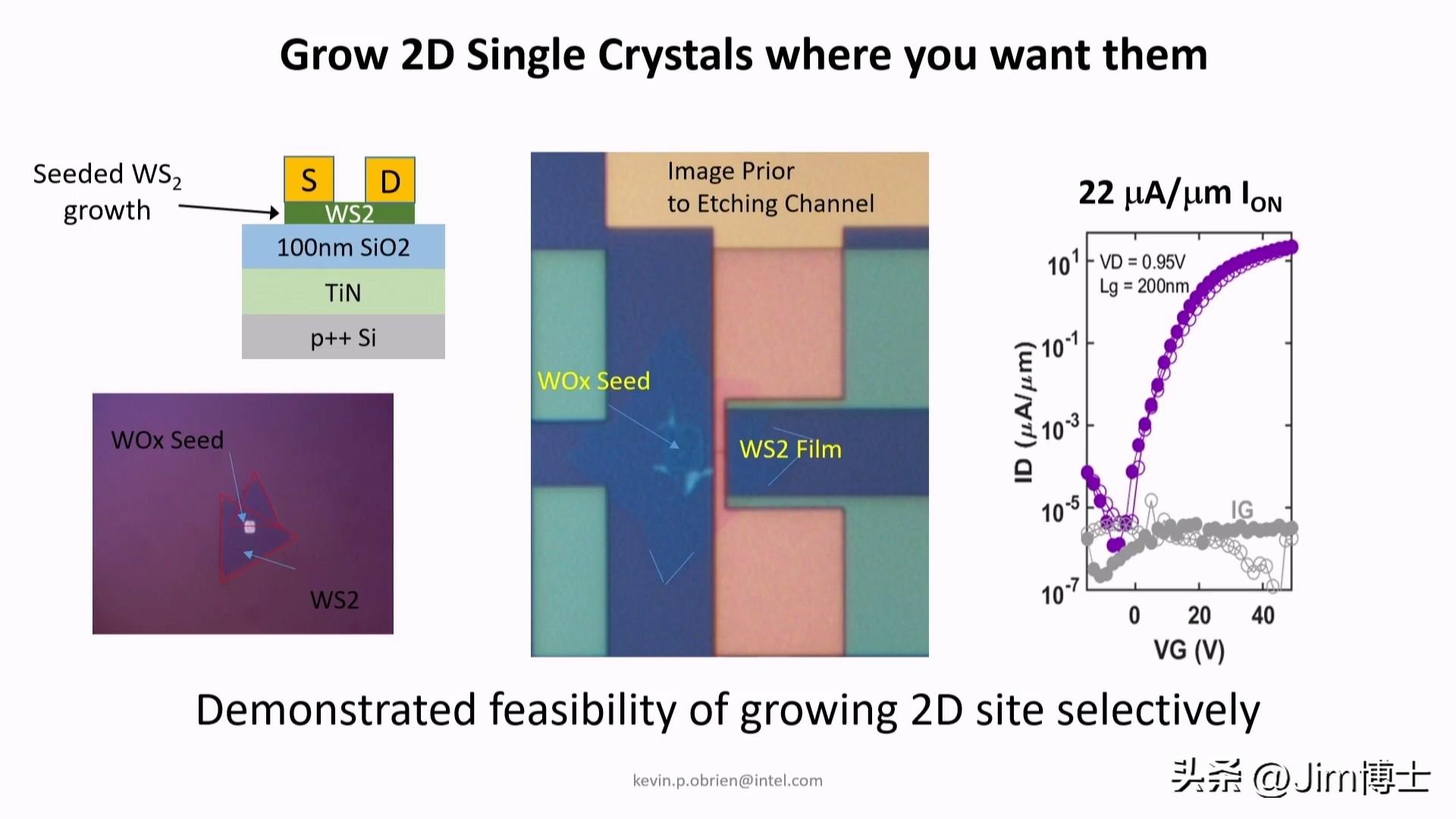

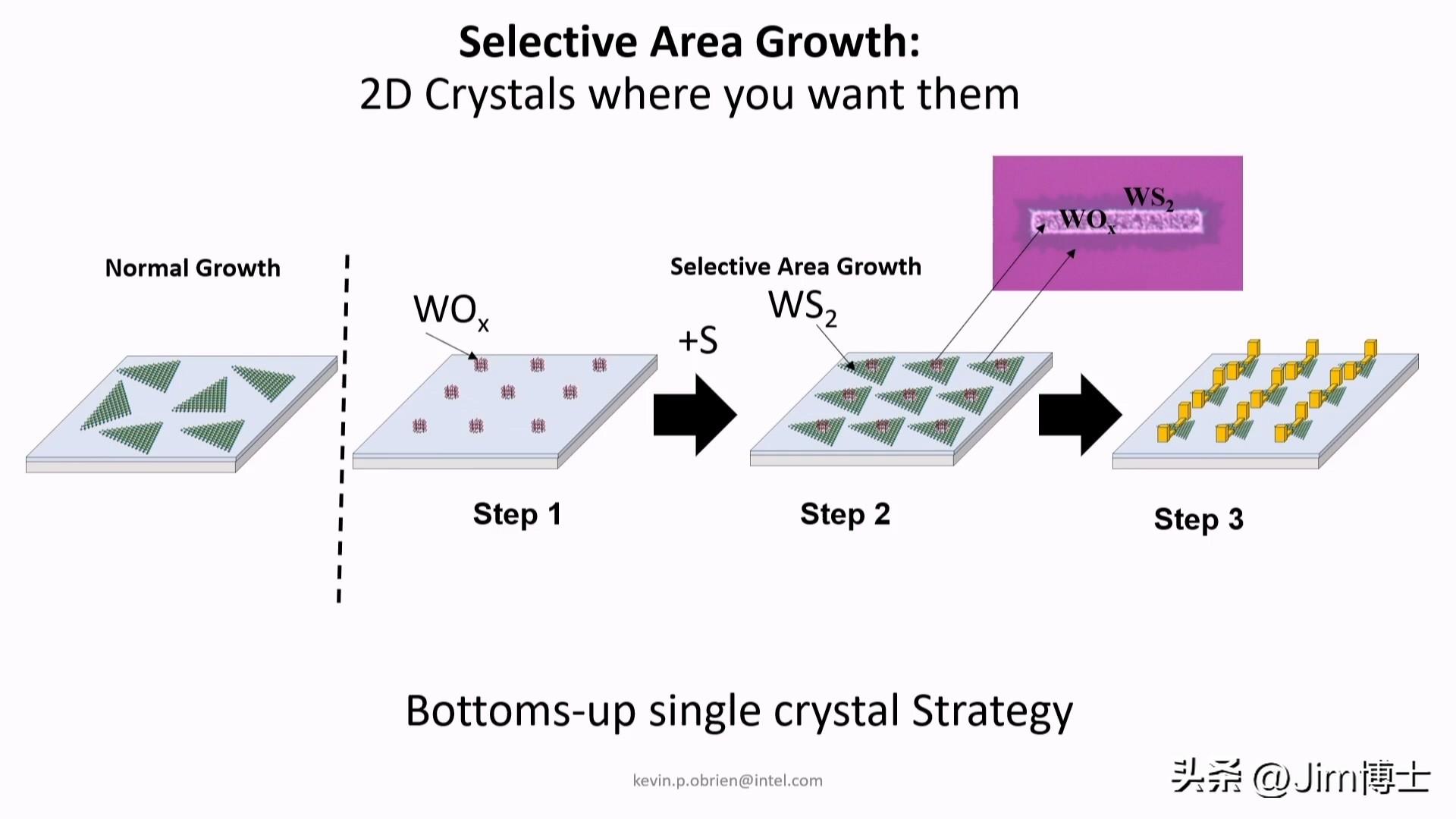

目前英特尔也只进行到了晶圆级的2D半导体材料的定向生长。这项工作采用的事选择性区域沉积法,在沟道位置通过沉积种子氧化物薄层,可以在其上选择沉积单层2D半导体。

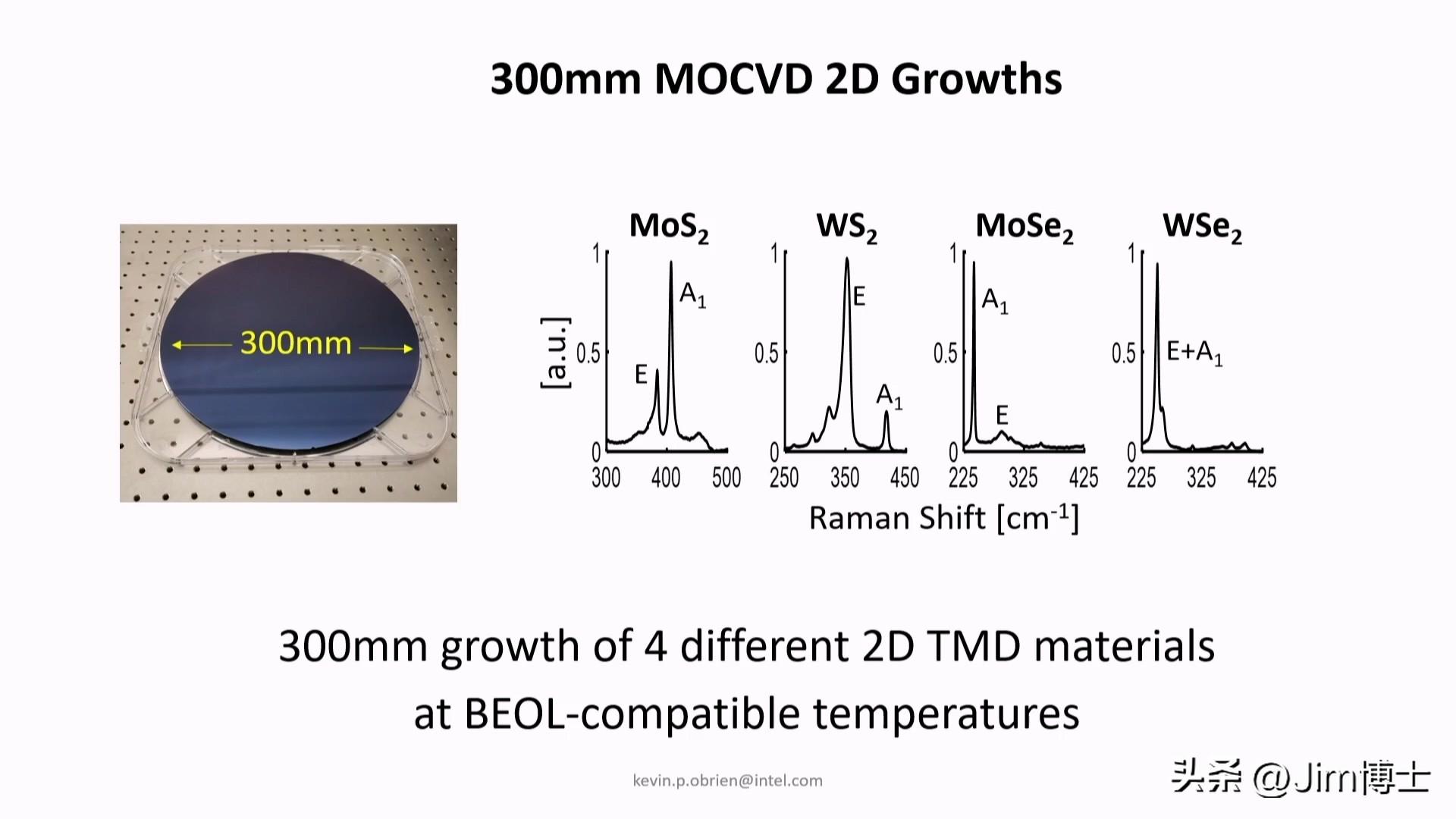

英特尔展示了在12寸晶圆上生长MoS2、WS2、MoSe2、WSe2等2D半导体。

当然,仅仅从材料学角度而言,目前普通的物理、化学实验室都具备类似的生长研究条件。

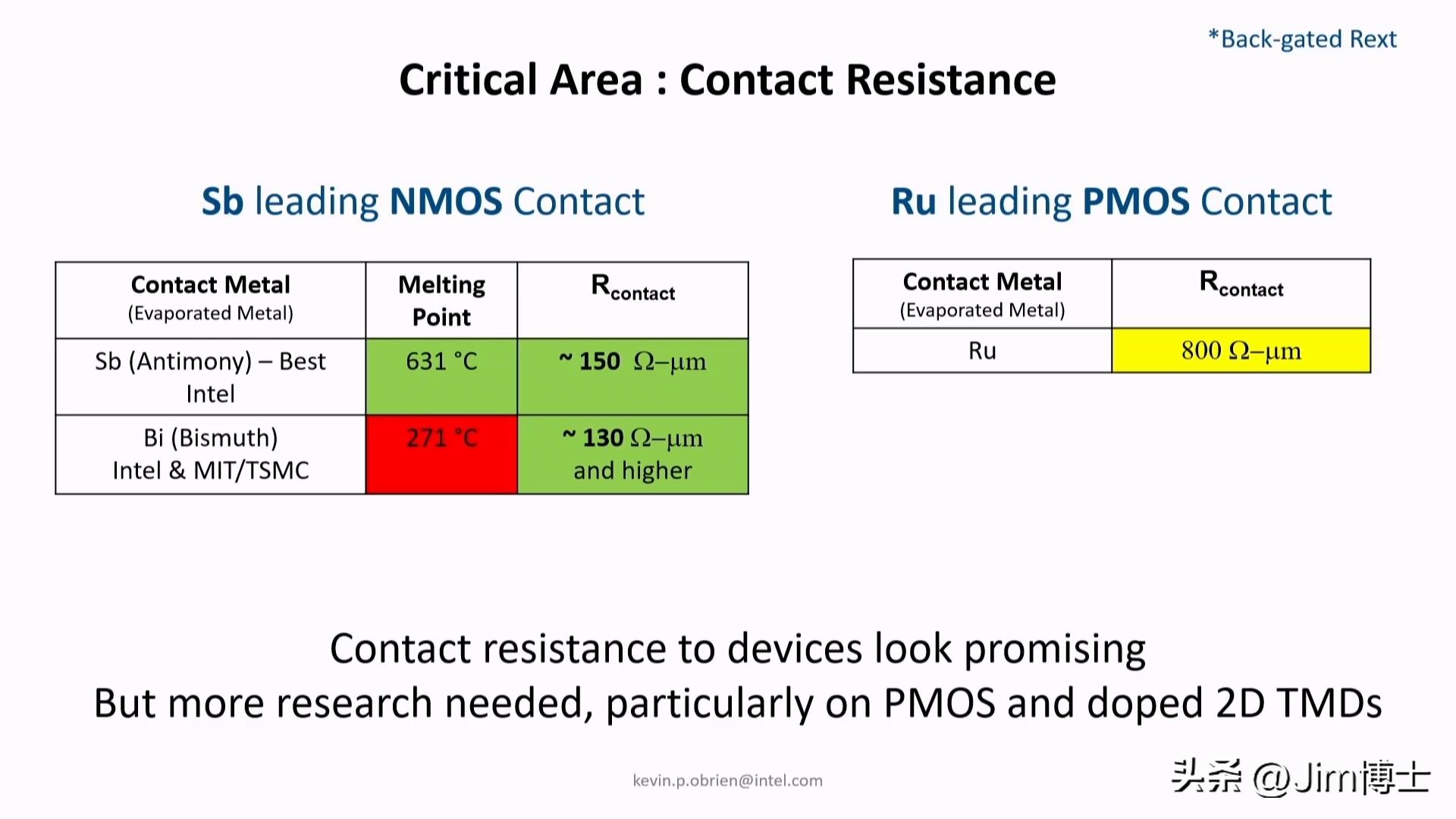

前面提到,2D材料在1纳米厚度的尺寸下,如何进行电连接是研究晶体管性能的关键,所以降低接触金属与2D材料的接触电阻是近期的一项重要工作。

我们近一两年看到的许多突破都来自于这个议题,比如此前英特尔采用了高温熔点的Sb作为接触金属,可以将NMOS接触电阻降低到150欧姆·微米;此后英特尔和台积电、麻省理工合作,采用金属Bi将NMOS接触电阻降低到更低的130欧姆·微米。

而在2D材料的PMOS接触金属金属中,金属Ru可以达到800欧姆·微米,因此还需要大量的创新优化。

毫无疑问,2D半导体芯片是未来十年半导体研究的热门领域,它要在极小的空间研究大量的集成、生长、界面、缺陷、掺杂、空间均匀性、晶界等问题。尽管从2010年石墨烯获得诺贝尔物理学奖以来,2D半导体材料成为研究热点,但是目前距离其实现超越硅芯片的0.2纳米芯片还有很长的路要走。

下篇我们继续聊!

鲁公网安备37020202000738号

鲁公网安备37020202000738号