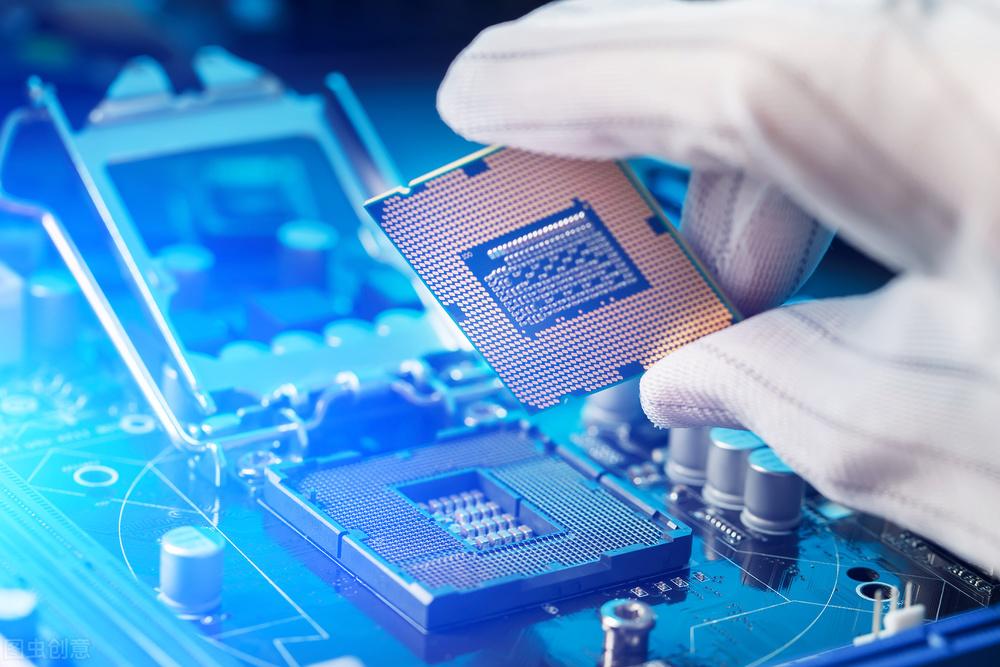

数字后端处于数字IC设计流程的后端,属于数字IC设计类岗位的一种。在IC设计中,后端设计的人数占比算是比较多的,并且随着芯片行业的不断发展,后端工程师的人才需求未来会越来越多。

数字后端的目的

数字前端设计:在集成电路设计中,从Verilog/VHDL代码(RTL级)编写验证再通过综合( synthesis)转换成门级网表( gate netlist)的过程。

数字后端设计(backend design):门级网表的物理实现,即把门级网表转换成版图。

完整的后端设计由后端半定制与后端全定制两个设计部分组成:

1)后端全定制设计是指在设计初期最先按照设计需求设计出的物理单元库,物理单元库由标准单元库、IP库及满足特殊需求的定制部件单元等组成。该物理库为后续后端半定制设计提供物理实现基础。

2)后端半定制设计是指使用布局布线工具并基于后端全定制阶段完成的标准单元库及IP库并根据前端设计完成整个芯片的组装与实现,这个过程又称为数字后端设计(自动布局布线-APR)。

传统上将布局布线前的工作称之为数字前端(Front End)设计,而将布局布线之后的工作称为数字后端(Back End)设计。

布局的目的在于产生制作掩膜所需的GDSII文件;同时也产生布局后的网表文件(Netlist)及标准延迟文件(SDF)。

运用给定的输入,在给定的时间内做出符合signoff条件的PR结果并满足各种验证。

岗位技能

软件工具

数字后端主要以软件工具为主,主要掌握以下软件(以cadence, synopsys,mentor公司为主):

布局布线:Innovus/Encounter, ICC2/ICC

综合:DC, Genus

物理验证:Calibre

静态时序分析:PrimeTime, Tempus

功耗分析:Redhawk, Voltus,PTPX

每种平台需要你掌握的技能不大一样,通常每种平台下学会一种工具即可。一个初级工程师想全部掌握这些技能也很难,如果这些工具你都会使用,就相当厉害了。

掌握工具主要是为了应用,后端设计要学会如何使用工具分析功耗及其对设计的影响(static/dynamic IR-drop, EM等)。学会使用工具分析和解决cross talk问题。

脚本语言

由于数字后端工程师需要跑一些自动化的任务,所以掌握脚本语言也是必须的,比如掌握下面的知识就显得比较重要:

Verilog

TCL

Perl

Python

其他技能

1、熟悉后端流程,(IO plan, floorplan, power flan, place, CTS, route);

2、精通时序分析;

3、理解后端常用库和文件的格式,内容,生成和转换,比如: .lib, spice, lef, def;

4、精通一种unix script语言,现在大多用perl,也可以用awk(TCL不是unix script语言,但是也一定要会);

5、十分了解circuit design及其工具 (为DRC/LVS准备的);

6、具备DFT的基本概念;

7、了解package design的种类和过程。

一个优秀的后端工程师要能够在复杂的结果中,识别出问题的真假,比如时序上的违反,找出解决问题或者防止问题发生的方法,然后灵活有效地使用工具来达到你的要求。

所有的技术类岗位,主要看的两点就是:专业技能(skills)和项目经验(experience)。所以除了上面列的这些技能,你能实际做过一两个项目,哪怕是一些小模块的后端设计,也是很重要的,尤其是做项目过程中积攒的debug经验。

数字后端设计工程师要做什么?

(1)逻辑综合(Synthesis)

主要负责将RTL code转换为实际后端使用的netlist网表, 一个好的网表对布局布线的工作起到决定性作用。要尽可能做到performance, power, area的优化。尤其是现如今的一些要求高性能的设计,对综合的要求非常高。

综合质量很大一定程度上取决于综合软件的性能,业界流行的两个综合工具是Synopsys的Design Compiler和Cadence的Genus,熟练的掌握两个工具的使用方法是综合工作的一个基本条件。

(2)布局布线(PD)

布局布线是数字后端中占比最大的工作,主要负责netlist到GDSII的转化过程,步骤包括Floorplan,Place,CTS,Optimize,Route,ECO等,确保自己负责的模块满足时序还有物理制造的要求。同时,需要协同其他工程师,及时提供他们需要的文件,比如def、 spef、网表等,是数字后端中最核心的工作。

布局布线对工具的依赖程度较强,而且工具操作相对来说较为复杂。业界较为常用的是cadence的Innovus软件和Synopsys的ICC,掌握这两大工具的使用需要花费一定的时间。

(3)静态时序分析(STA)

静态时序分析简称为STA,时序验证分析是数字后端中的重要一块内容,芯片需要满足各种corner下面的setup,hold时序要求以及其他的transition, capacitance, noise等要求。STA需要制定整个芯片的sdc约束文件,选择芯片需要signoff的corner以及全芯片的timing eco流程。是一份难度要求很高的工作。

静态时序分析通常通常需要掌握Synopsys的primetime以及cadence的tempus两大软件的使用方法。

(4)物理验证(PV)

物理验证也是tape out前的一项重要事项。如果物理验证有错,那芯片生产就会失败。在布局布线工具中,软件只能检查到金属层上的物理违反,而真正的物理验证需要检查到器件底层(base layer)。

因此,物理验证需要将金属层和底层金属合并到一起,进行全芯片的drc检查。同时,还需要做全芯片的LVS(版图与原理图一致性检查),ERC(电气规则检查)。确保芯片没有任何物理设计规则违反。

物理验证一般在mentor公司的calibre中进行,是业界标准的物理验证工具。

(5)功耗分析(PA)

功耗分析也是芯片signoff的重要一大块,随着现在芯片的规模越来越大,功耗在芯片的中的地位也越来越高。功耗分析的两大任务是分析IR drop(电压降)和EM(电迁移)。及时将结果反馈给布局布线任务组,让他们及时修改后端设计图,解决设计中潜在的问题。

一般功耗分析使用的工具有Ansys公司的redhawk,以及cadence公司的voltus和synopsys公司的ptpx。

总而言之,数字IC后端设计在芯片设计的过程中是举足轻重的,每个岗位都有自己的特点,想要入行的朋友,一定要多学习,提升自己的能力,这样才能在工作不断提升能力,学习之路上,IC修真院与你同行。

更多内容可查看https://ic.coachip.cn/

鲁公网安备37020202000738号

鲁公网安备37020202000738号