如果说京东的笔试题写着“不缺人”,那么阿里的笔试题就是告诉你“你是智障”。

秋招的同学们发来这样的哀嚎,好笑之余,小编决定开启助力秋招笔试的系列,特别邀请嘉宾,为大家解析各大公司笔试高频题,帮助在为秋招发愁,毕业找工作哭泣的准毕业生们!

笔试,基本是校招的必经之路,只有通过这一关,才有可能进入到面试,直到最终被录取。近年来,人才竞争激烈,招聘的要求也越来越高,尤其是大公司,笔试题也越来越难,考察的内容也越来越全面,但这些公司的笔试题都是有题库的。

我们通过网上朋友的笔试回忆,对这些实战过的题目来做解析,这些真题最有价值,也最具说服力。我们的目的不仅仅在于对本题目本身答案的解析,更是深入到原理、方法的讲解,最关键的是还会对相关的知识进行扩展,让你学到更多。无论你是刚开始学习的小白,还是正在苦苦求职的毕业生,或是打算继续深耕技术,这个系列都可以满足你。积少成多,集腋成裘,只要我们坚持,总会有成为大牛的一天!

我们讲解的题目不多,但会涉及到选择、填空、问答、编程,接下来就让我们一起来看一下今天的题目吧。大家不看解析,先自己做一下题目,然后再对照答案,毕竟都是真题可不能浪费呦!最后通过解析看看你是否在做对的同时也想到这么多呢!

━ ━ 我是一条有技术的分割线 ━ ━

今天正式开始笔试题目解析第一弹,我们选择华为硬件逻辑岗的题目,原因是华为的题目考核的能力全面,涉及到模电,数电,数字信号处理,通信,IC,FPGA等各类题,很有参考意义,每年为华为挤破头的同学也是前赴后继。

1、十进制46.25对应的二进制表达式为( )。(华为硬件逻辑实习岗)

A 101110.11 B 101101.01

C 101110.1 D 101110.01

解析:

这个问题看上去很简单,那是因为我们平时可以打开电脑上的计算器,然后用程序员功能立刻就能出结果,但是笔试的时候我们并不能使用这种“作弊”的功能,所以还是要会手算。可能很多同学数电是大一大二时学习的,很久没有接触过这么基础的问题了,那就让我们一起来回忆下吧。

首先这个题目是由整数部分和小数不同共同组成的,整数部分的计算是最简单的,整数部分除以2得到的余数按照逆向顺序排列后就是整数部分转化为二进制后的结果,详细过程如下所示:

46转化为二进制的结果就是101110

小数部分的计算可能很多人记不清楚了,小数部分每次乘以2后得出的结果取其整数部分,直到小数部分为0或达到精度要求为止,详细过程如下所示:

0.25转化为二进制的结果就是.01

综上所述,最后的答案选择D 101110.01

2、在时序电路的状态转换表中,若状态数N=3,则状态变量数最少为( ) (华为硬件逻辑实习岗)

A 4 B 8 C 2 D 16

解析:

让我们先看一下一个完整的状态机代码都有哪些内容:

//-----------------------

01module simple_fsm(

02input wire sys_clk , //系统时钟50Mhz

03input wire sys_rst_n , //全局复位

04input wire pi_money , //投币方式可以为:不投币(0)、投1元(1)

05

06output reg po_cola //po_cola为1时出可乐,po_cola为0时不出可乐

07);

08

09//只有三种状态,使用独热码

10parameter IDLE =3'b001;

11parameter ONE =3'b010;

12parameter TWO =3'b100;

13

14reg [2:0] state;

15

16//第一段状态机,描述当前状态state如何根据输入跳转到下一状态

17always@(posedge sys_clk ornegedge sys_rst_n)

18if(sys_rst_n ==1'b0)

19 state<= IDLE;

20elsecase(state)

21 IDLE : if(pi_money ==1'b1)//判断输入情况

22 state<= ONE;

23 else

24 state<= IDLE;

25

26 ONE :if(pi_money ==1'b1)

27 state<= TWO;

28 else

29 state<= ONE;

30

31 TWO : if(pi_money ==1'b1)

32 state<= IDLE;

33 else

34 state<= TWO;

35

36 default: state <= IDLE;

37 endcase

38

39//第二段状态机,描述当前状态state和输入pi_money如何影响po_cola输出

40always@(posedge sys_clk ornegedge sys_rst_n)

41if(sys_rst_n == 1'b0)

42 po_cola<=1'b0;

43else if((state == TWO)&&(pi_money ==1'b1))

44 po_cola<=1'b1;

45else

46 po_cola<=1'b0;

47

48endmodule

//-----------------------

上面是一个用Verilog描述的简单状态机,其功能是每次只能输入1元硬币,输入3元时出可乐,其中01-07行是端口列表部分,10-12行是状态编码部分,14行是定义的状态变量,17-37行是第一段状态机部分,40-46是第二段状态机部分。

题目中说状态数有3个,状态变量数最少为多少(此处应该是指位宽)?上面的例子中10-12行是状态编码,即有多少个状态数就需要有多少个状态编码,这里一共有3种;14行是状态变量,这里为什么状态变量的位宽是3呢?因为我们采用了独热码的编码方式,每个状态数只有1比特为1,其余比特都为0,所以3个状态就要用3位宽的变量,如果是4个状态那就要用4位宽的变量,也就是一共有几个状态数就需要几位宽的状态变量。而题目中说的是“最少“,那么除了我们用独热码的方式对状态进行编码,还有其他的方法吗?答案是当然。我们还可以采用二进制码或格雷码的方式对状态进行编码,上面的例子中如果我们用二进制码编码3个状态则为:2‘b00,2‘b01,2‘b10;而用格雷码编码3个状态则为:2‘b00,2‘b01,2‘b11,都只需要2位宽的状态变量即可,即便是有4个状态数,我们使用2位宽的状态变量依然可以解决问题,要比独热码更节省状态变量的位宽个数。所以这里答案选择C 2。

讲到这里并没有结束,我们稍微拓展一下让大家学到更多。为什么例子中我们使用的是独热码而非二进制码或格雷码呢?那就要从每种编码的特性上说起了,首先独热码因为每个状态只有1bit是不同的,所以在执行到43行时的(state == TWO)这条语句时,综合器会识别出这是一个比较器,而因为只有1比特为1,所以综合器会进行智能优化为(state[2] == 1’b1),这就相当于把之前3比特的比较器变为了1比特的比较器,大大节省了组合逻辑资源,但是付出的代价就是状态变量的位宽需要的比较多,而我们FPGA中组合逻辑资源相对较少,所以比较宝贵,而寄存器资源较多,所以很完美。而二进制编码的情况和独热码刚好相反,他因为使用了较少的状态变量,使之在减少了寄存器状态的同时无法进行比较器部分的优化,所以使用的寄存器资源较少,而使用的组合逻辑资源较多,我们还知道CPLD就是一个组合逻辑资源多而寄存器逻辑资源少的器件,因为这里我们使用的是FPGA器件,所以使用独热码进行编码。就因为这个比较部分的优化,还使得使用独热码编码的状态机可以在高速系统上运行,其原因是多比特的比较器每个比特到达比较器的时间可能会因为布局布线的走线长短而导致路径延时的不同,这样在高速系统下,就会导致采集到不稳定的状态,导致比较后的结果产生一个时钟的毛刺,使输出不稳定,而单比特的比较器就不用考虑这种问题。下面是示意图解析:

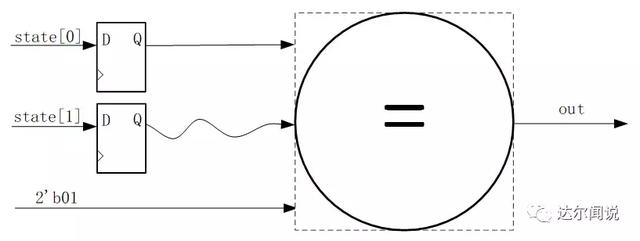

单比特比较器示意图

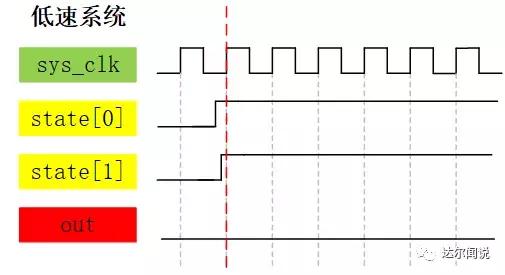

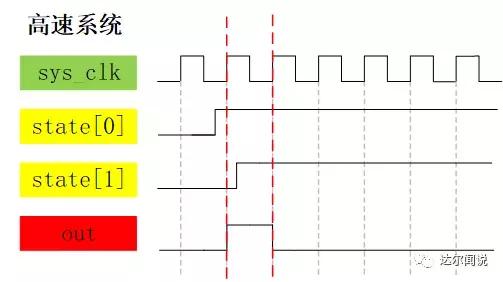

单比特比较器波形图

多比特比较器示意图

低速系统下多比特比较器波形图

高速系统下多比特比较器波形图

用独热码编码虽然好处多多,但是如果状态数非常多的话即使是FPGA也吃不消独热码对寄存器的消耗,所以当状态数特别多的时候可以使用格雷码对状态进行编码。格雷码虽然也是和二进制编码一样使用的寄存器资源少,组合逻辑资源多,但是其相邻状态转换时只有一个状态发生翻转,这样不仅能消除状态转换时由多条信号线的传输延迟所造成的毛刺,又可以降低功耗,所以要优于二进制编码的方式,相当于是独热码和二进制编码的折中。

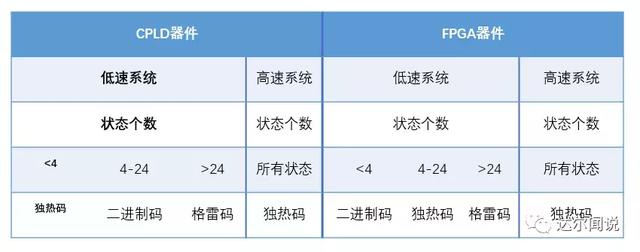

最后我们用一个表格来总结一下什么时候使用什么方式的编码效果最好(有时候不管你使用哪种编码方式,综合器会根据实际情况在综合时智能的给你进行编码的转换,当然这需要你设置额外的综合约束,这里我们不再详细讲解) 。

课后作业及预告:下一期我们将对下面的题目进行详细的扩展解析,大家可以提前做一下,敬请期待……

1、只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容 ( )。(华为硬件逻辑实习岗)

A 全部为0 B 不可预料

C 保持不变 D 全部改变

2、在Verilog语言中,a = 4’b1011,那么&a为( )。(华为硬件逻辑实习岗)

A 4’b1111 B 1’b1

C 1’b0 D 4’b1011

鲁公网安备37020202000738号

鲁公网安备37020202000738号