2021年6月,IBM宣布实现12英寸晶圆制造2纳米芯片,开启了半导体制程的新时代。

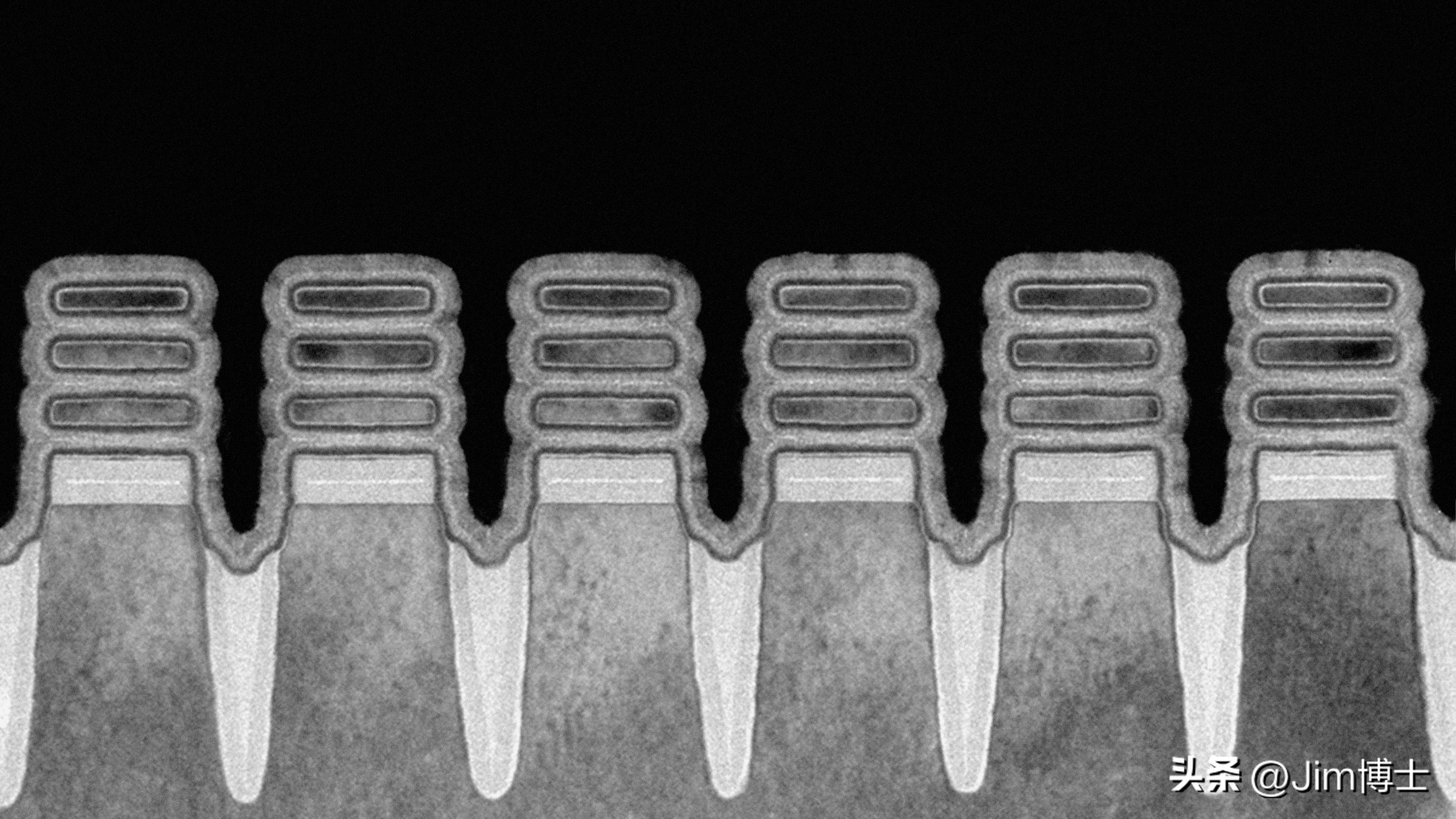

下图是著名的“2纳米”芯片的晶体管的透射电镜剖面图,你几乎可以在任何一篇介绍2纳米芯片的文章里看见它:

它展示了众所周知的GAA晶体管的沟道结构和栅极结构。

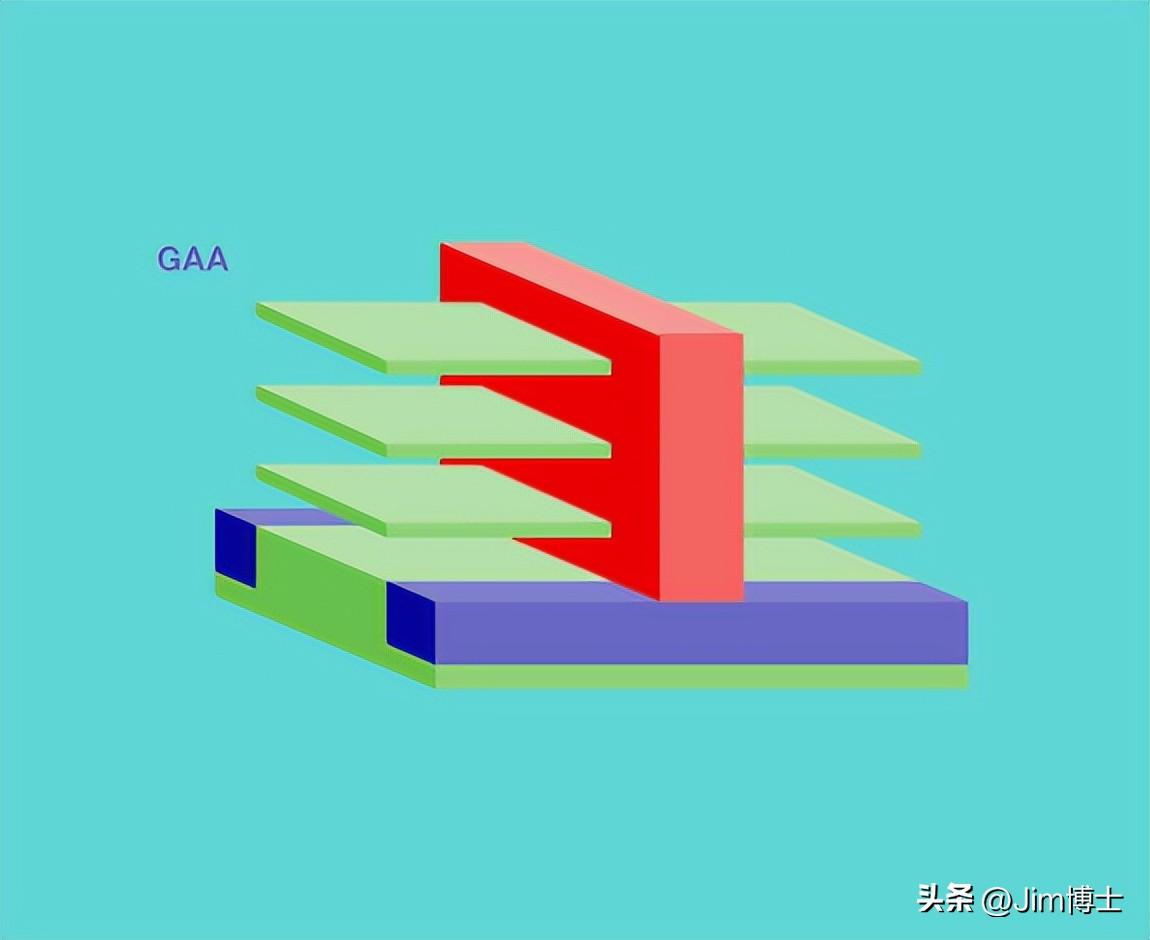

上面这幅经典的GAA构架晶体管照片中,包含了3个沟道。我们可以在下面这张立体示意图中更清晰的看到3个沟道(channel,绿色翅片)的空间位置。

IBM指出沟道宽度可以从45纳米降低到15纳米。

实际上,2012年IBM首次使用“纳米片”(Nanosheet)来描述这种新的芯片构架。到2021年实现2纳米芯片,已经过去了10年。

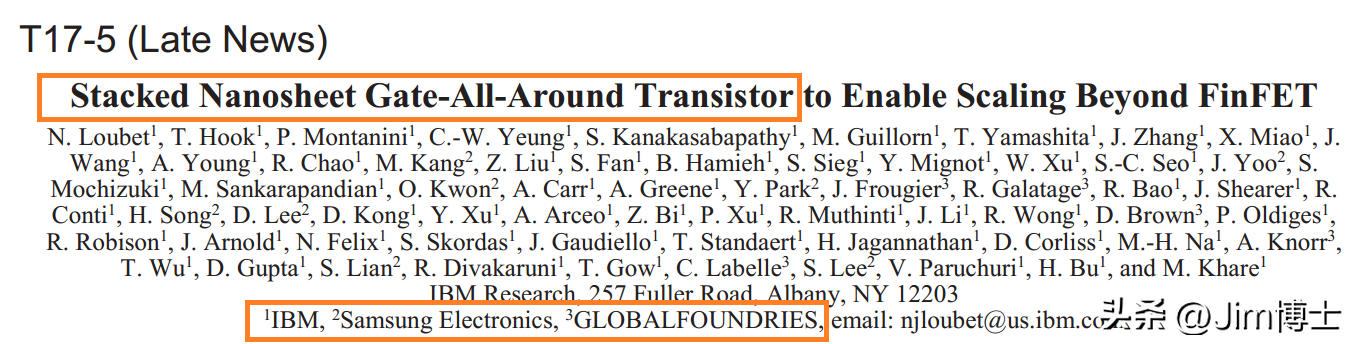

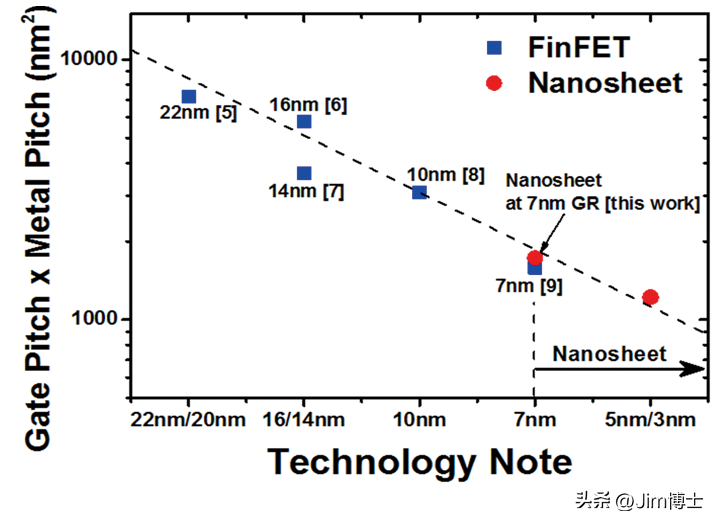

而技术上真正的突破,则发生在2017年--彼时,IBM和合作伙伴三星电子、格芯发表论文,成功实现了GAA构架晶体管,并证明了其在7纳米芯片节点以下仍然可以实现超越FinFET构架的节点缩放能力。

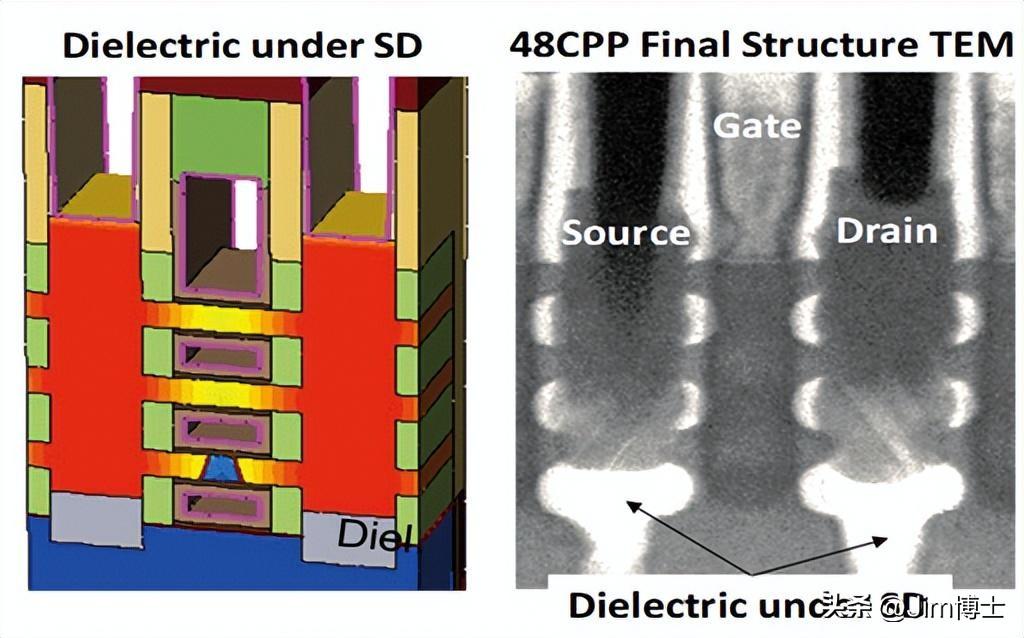

下图是5纳米的GAA晶体管结构的横截面图,它展示了栅极(Gate)和源漏极结构。

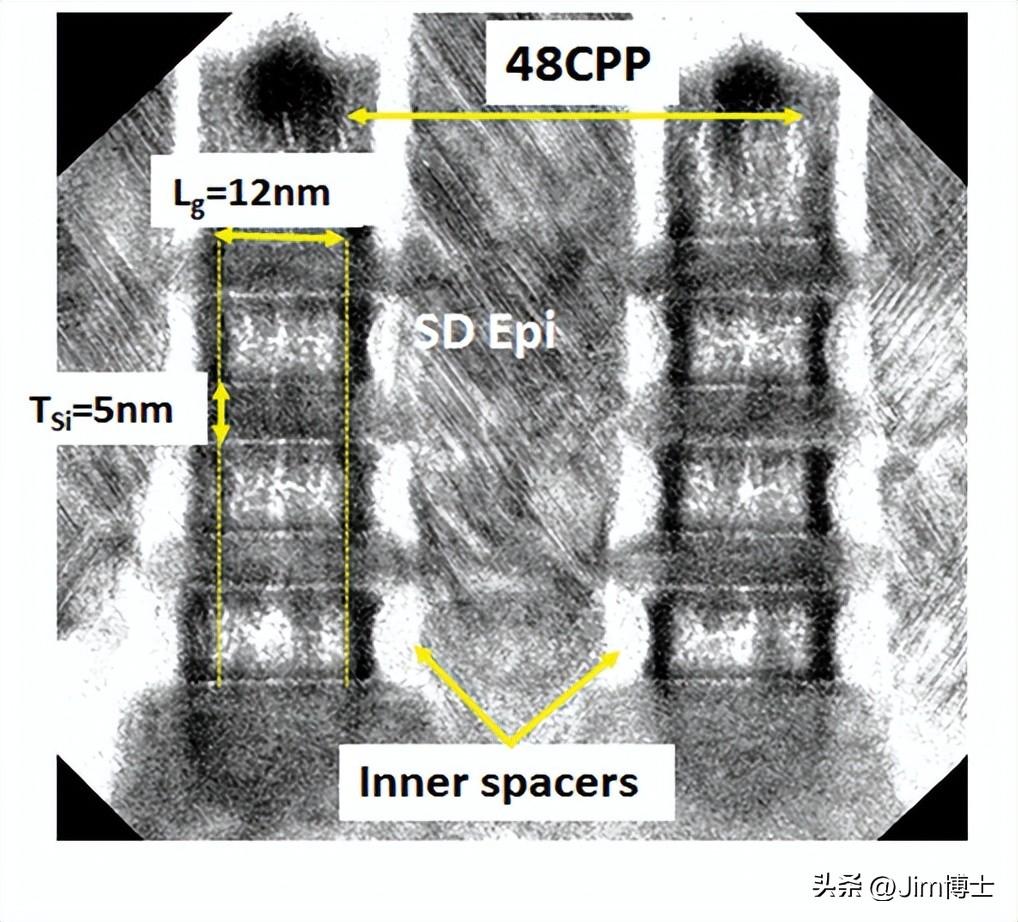

下面这张电镜照片中,标记了5纳米的GAA晶体管的结构尺寸:

1,它包括3层沟道,厚5纳米;

2,栅极宽度(Lg)是12纳米;

3,栅极间距(CPP)是48纳米。

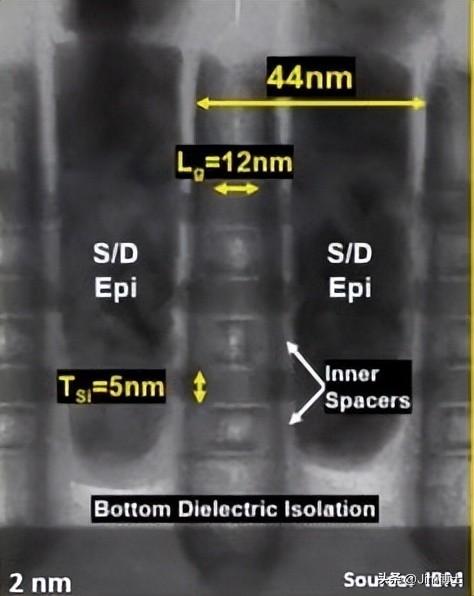

下图是2021年IBM发布的2纳米GAA晶体管的电镜图,我们可以看到,其结构与2017年发表的5纳米GAA晶体管结构图非常接近:

1,它同样包括3层沟道,厚5纳米;

2,它的栅极宽度(Lg)也是12纳米;

3,不同的是,2纳米GAA芯片的栅极间距(CPP)是44纳米。

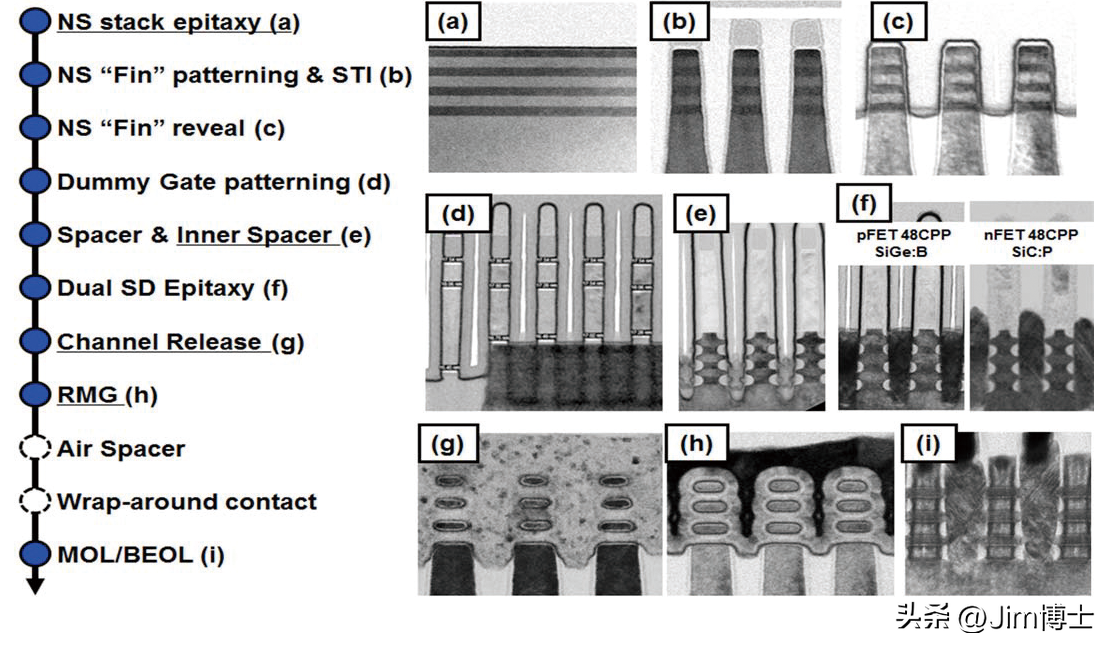

那么这种多层沟道被4面包围的结构是如何实现的呢?它的工艺其实是采用了多层外延交替膜来制造的。也就是类似EUV光刻机的反射镜多层膜一样,在晶圆上交替生长几个纳米的硅和锗硅,再以CMOS工艺进行加工形成GAA晶体管的基本的堆栈结构。

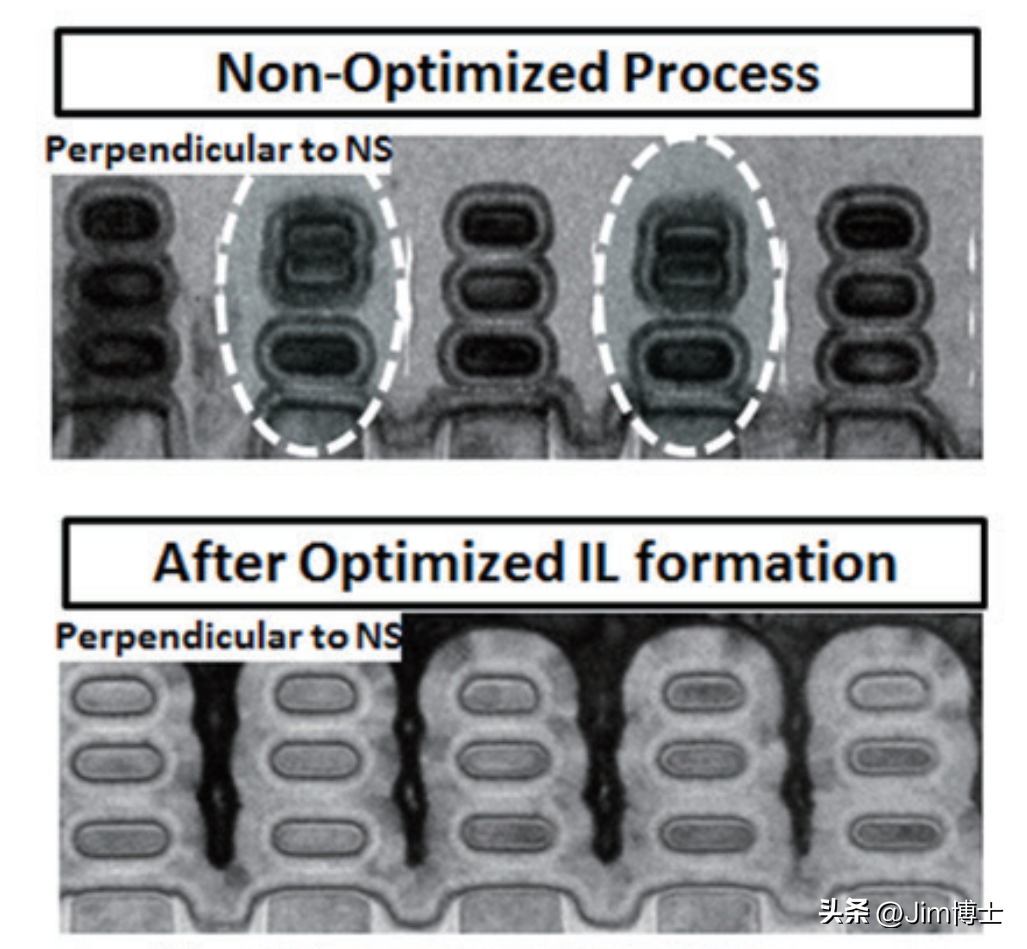

对于GAA的堆叠结构,需要对工艺流程进行大量优化,下图比较了优化前和优化后的3堆栈堆叠的电镜图,其中差距一目了然。

IBM的2纳米芯片研究工作是在美国纽约奥尔巴尼的IBM研究院完成的。

这里是全美芯片研究的中心之一,它在2006年引进了ASML的第一台EUV光刻演示工具,目前安装了ASML的最先进的EUV光刻机。

接下来我们继续探索IBM如何实现2纳米芯片的制造!

鲁公网安备37020202000738号

鲁公网安备37020202000738号